ARM Announces Cortex-A32 IoT and Embedded Processor

by Andrei Frumusanu on February 22, 2016 7:01 PM EST- Posted in

- Mobile

- Arm

- Embedded

- IoT

- Cortex A32

Today ARM announces the new Cortex A32 ultra-low power/high efficiency processor IP. For some readers this might come as a surprise as it's only been a few months since we saw the announcement of the Cortex A35 which was presented as a replacement for the Cortex A7 and A5, so this leaves us with the question of where the Cortex A32 positions itself against both past IPs such as the A7 and A5, but also how it compares against the A35.

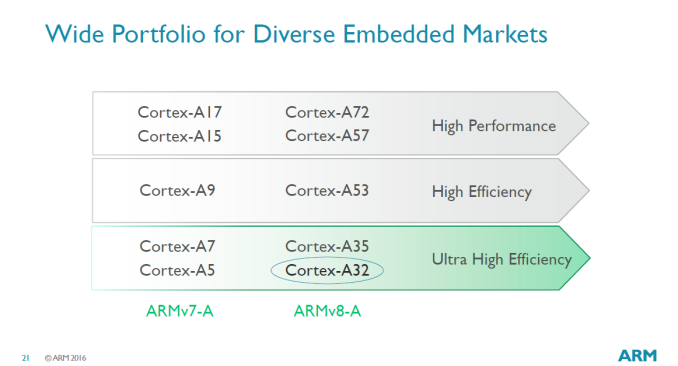

The answer is rather simple: It's still a replacement for the A7 and A5, but targets even lower power use-cases than what the A35 was designed for. While ARM sees the A35 as the core for the next billion low-end smartphones, the A32 seems to be more targeted at the embedded market. In particular it's the "Rich Embedded" market that ARM seems to be excited about. The differentiation lies between use-cases which require a full-fledged MMU and thus able to run full operating systems based on Linux, and those who don't and could make due with a simpler micro-controller based on one of ARM's Cortex-M profile IPs. It's also worth to mention that although last time we claimed that the A35 would servce the IoT market, ARM seems to see wearables and similar devices as part of the "Rich Embedded" umbrella-term and thus now it seems more likely that it's the A32 that will be the core that will power such designs.

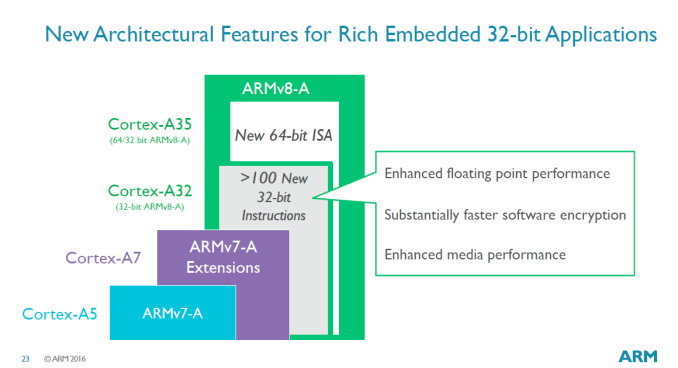

This leads us to the mystery of what exactly is the A32? During the briefing the only logical question that seemed to come to mind is: "Is this an A35 with 64-bit 'slashed off'?" While ARM chuckled at my oversimplification, they agreed that from a very high-level perspective that it could be considered as an accurate description of the A32.

In more technical terms, the A32 is an 32-bit ARMv8-A processor with largely the same microarchitectural characteristics of the Cortex A35. As a reminder to our readers out there: The ARMv8 ISA is not only an 64-bit instruction set but also contains many improvements and additions to the 32-bit profile commonly named as AArch32. Among the larger differences between the A35 and A32 is that the latter's microarchitecture has been tuned and optimized to achieve the best performance and efficiency for 32-bit.

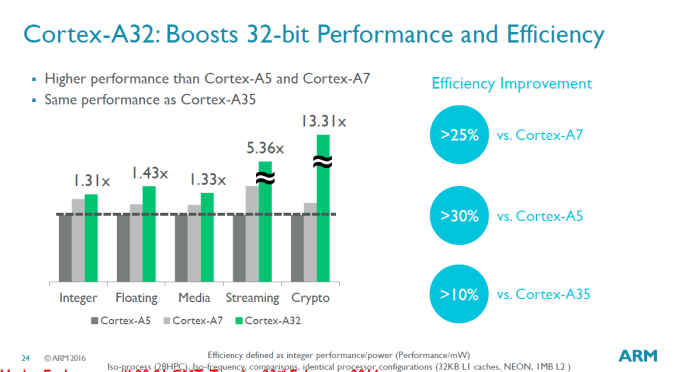

Indeed, performance wise, the A32 is advertised as being able to match the Cortex A35. The improvements lie in power efficiency: as a result of dropping its 64-bit capabilities, the new core is now able to achieve up to 10% better efficiency than the Cortex A35. Similarly to the A35, the A32 promises to achieve vastly superior performance per clock versus the Cortex A5 and A7, achieving anywhere from a 31% increase in integer workloads to a massive factor of 13x in crypto workloads, which the A32 is still capable of as they're included in the AArch32 ARMv8 profile.

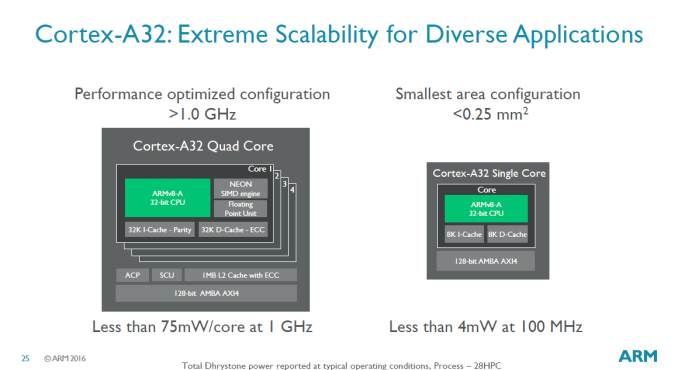

While only a few months ago the Cortex A35 was advertised as ARM's smallest Cortex-A core, this title has now been passed on to the A32. ARM claims the core is around 30% smaller than the A35; The decrease in size, mostly due to the slimming down of the micro-architecture due the removal of 64-bit capability, allows the Cortex A32 to scale down to <0.25mm² in its smallest configuration, a significant decrease compared to the A35's disclosed <0.4mm². The core remains as configurable as the Cortex A35, able to run as either as single core or any as a cluster up to four cores. Optionally vendors can also configure cache sizes, with L1 ranging from 8KB to 32KB and L2 either being completely absent to up to 1MB in size.

ARM's philosophy of "having the right design for the job" now seems more apparent than ever as we see an steadily increasing portfolio of processor IPs specialized for different use-cases. The A32 seems to fit right in with this strategy and we'll more than certainly see a large array of devices powered by the core in the future to come.

27 Comments

View All Comments

coburn_c - Monday, February 22, 2016 - link

'ultra-low efficiency'I though AMD had that market sewn up?

coburn_c - Monday, February 22, 2016 - link

Also, dropping 64-bit support is now an advancement?I told you so, I told you so, I told you so.

coburn_c - Monday, February 22, 2016 - link

Also, also; does this mean that gentleman at Qualcomm can have his job back?xdrol - Tuesday, February 23, 2016 - link

If you don't use all 64 bit memory addresses, then AArch32 even could perform better than AArch64 with its smaller program footprint and memory/cache usage, and I guess both is a plus in the ultra-mega low power world. (Noticed that all categories are 'high' in marketing lingo?)tuxRoller - Tuesday, February 23, 2016 - link

It's not just addresses but registers, as well.tuxRoller - Tuesday, February 23, 2016 - link

OTOH, you could use the x32abi of the x64isa to get access to those additional registers without incurring the pointer penalty (ofc you also wouldn't have access to the 64bit address space).extide - Wednesday, February 24, 2016 - link

That's exactly what AArch32 in ARM v8 is.0x16a0 - Friday, February 26, 2016 - link

No, ABI is separate to the architecture. The equivalent of x32 ABI for ARM is ILP32.AArch32 has 32 bit registers and 32 bit pointers.

kgardas - Tuesday, February 23, 2016 - link

I don't think so, the reason is bigger register set on AArch64. You used word "perform" so I've thought this is from pure performance point of view. On the other hand efficiency is another thing to consider here, and that's what A32 is about...boeush - Tuesday, February 23, 2016 - link

Kinda crazy, next thing you know, they'll start making mobile devices with reasonable screen resolutions again - achieving earth-shattering improvements in performance, battery life, and efficiency...